# Evaluation of Machine Learning Primitives on a Digital Signal Processor

Vilhelm Engström

2020-06-12

# **Evaluation of Machine Learning Primitives on a Digital Signal Processor**

Examensarbete utfört i Datateknik vid Tekniska högskolan vid Linköpings universitet

Vilhelm Engström

Handledare Gabriel Eilertsen Examinator Aida Nordman

Norrköping 2020-06-12

### Upphovsrätt

Detta dokument hålls tillgängligt på Internet – eller dess framtida ersättare – under en längre tid från publiceringsdatum under förutsättning att inga extraordinära omständigheter uppstår.

Tillgång till dokumentet innebär tillstånd för var och en att läsa, ladda ner, skriva ut enstaka kopior för enskilt bruk och att använda det oförändrat för ickekommersiell forskning och för undervisning. Överföring av upphovsrätten vid en senare tidpunkt kan inte upphäva detta tillstånd. All annan användning av dokumentet kräver upphovsmannens medgivande. För att garantera äktheten, säkerheten och tillgängligheten finns det lösningar av teknisk och administrativ art.

Upphovsmannens ideella rätt innefattar rätt att bli nämnd som upphovsman i den omfattning som god sed kräver vid användning av dokumentet på ovan beskrivna sätt samt skydd mot att dokumentet ändras eller presenteras i sådan form eller i sådant sammanhang som är kränkande för upphovsmannens litterära eller konstnärliga anseende eller egenart.

För ytterligare information om Linköping University Electronic Press se förlagets hemsida http://www.ep.liu.se/

### Copyright

The publishers will keep this document online on the Internet - or its possible replacement - for a considerable time from the date of publication barring exceptional circumstances.

The online availability of the document implies a permanent permission for anyone to read, to download, to print out single copies for your own use and to use it unchanged for any non-commercial research and educational purpose. Subsequent transfers of copyright cannot revoke this permission. All other uses of the document are conditional on the consent of the copyright owner. The publisher has taken technical and administrative measures to assure authenticity, security and accessibility.

According to intellectual property law the author has the right to be mentioned when his/her work is accessed as described above and to be protected against infringement.

For additional information about the Linköping University Electronic Press and its procedures for publication and for assurance of document integrity, please refer to its WWW home page: http://www.ep.liu.se/

#### Abstract

Modern handheld devices rely on specialized hardware for evaluating machine learning algorithms. This thesis investigates the feasibility of using the digital signal processor, a part of the modem of the device, as an alternative to this specialized hardware. Memory management techniques and implementations for evaluating the machine learning primitives convolutional, max-pooling and fully connected layers are proposed. The implementations are evaluated based on to what degree they utilize available hardware units. New instructions for packing data and facilitating instruction pipelining are suggested and evaluated. The results show that convolutional and fully connected layers are well-suited to the processor used. The aptness of the convolutional layer is subject to the kernel being applied with a stride of 1 as larger strides cause the hardware usage to plummet. Max-pooling layers, while not ill-suited, are the most limited in terms of hardware usage. The proposed instructions are shown to have positive effects on the throughput of the implementations.

### Acknowledgments

The author would like to thank MediaTek Inc. for the opportunity to work with them and their hardware throughout the thesis. Special thanks to Erik Bertilsson and Henrik Abelsson for providing guidance and feedback during the course of the work. Thanks are extended also to supervisor Gabriel Eilertsen and examiner Aida Nordman for being readily available whenever needed, be it for meetings, feedback, advice or just general discussion.

### Contents

| Al | stract                                                                                                                                                   | i                                                                                  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| A  | nowledgments                                                                                                                                             | ii                                                                                 |

| Co | itents                                                                                                                                                   | iii                                                                                |

| Li | of Figures                                                                                                                                               | v                                                                                  |

| Li | of Tables                                                                                                                                                | ix                                                                                 |

| 1  | Introduction1.1Motivation1.2Aim1.3Research Questions1.4Method at a Glance1.5Delimitations                                                                | 1<br>2<br>2<br>2<br>2                                                              |

| 2  | 1 5                                                                                                                                                      | 4<br>7<br>11<br>20<br>24<br>27                                                     |

| 3  | 3.2       Convolutional Layer         3.3       Max-Pooling Layer         3.4       Fully Connected Layer         3.5       Added Processor Instructions | <ul> <li>31</li> <li>33</li> <li>39</li> <li>43</li> <li>46</li> <li>47</li> </ul> |

| 4  | 4.1Memory Management4.2Convolutional Layer4.3Max-Pooling Layer4.4Fully Connected Layer                                                                   | <b>49</b><br>49<br>49<br>50<br>52<br>52                                            |

| 5  | 5.1 Results                                                                                                                                              | <b>54</b><br>54<br>57                                                              |

|    | 5.3 The Work in a Wider Context               | 60              |

|----|-----------------------------------------------|-----------------|

| 6  | Conclusion         6.1       Future Work      | <b>62</b><br>62 |

| Bi | bliography                                    | 64              |

| Α  | Proofs of Correctness         A.1 Convolution | 73              |

## List of Figures

| 2.1<br>2.2 | Scalar components of a second order tensor visualized in a matrix-like structure Application of a $3 \times 3$ convolution filter to a $3 \times 3$ image. a) The input image. b) The filter kernel. c) Application of the filter kernel to the input image in order to | 5        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.3        | produce a convolved feature. $\dots$ Application of a 3 × 3 cross-correlation filter to a 3 × 3 image. a) The input image.                                                                                                                                              | 6        |

|            | b) The filter kernel. c) Application of the filter kernel to the input image and the                                                                                                                                                                                    |          |

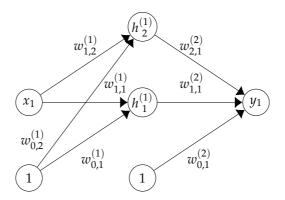

| 2.4        | resulting output.                                                                                                                                                                                                                                                       | 8        |

| 2.4        | A feedforward neural network with a single input, a single output and two hidden<br>layers, each of which consisting of three neurons. The superscripts of the hidden<br>neurons indicate to which layer they belong and the subscripts their index in said             |          |

| 2 5        | layer. Neither weights nor biases are shown.                                                                                                                                                                                                                            | 8        |

| 2.5        | Input and first hidden layer of the network shown in Fig. 2.4 with added weights.<br>The superscripts of the weights denote which layer the neuron at the end of the<br>edge belongs to. The subscripts indicate which neurons in the two layers are con-               |          |

|            |                                                                                                                                                                                                                                                                         | 9        |

| 2.6        | nected                                                                                                                                                                                                                                                                  |          |

|            | input neuron is its value, 1, multiplied with its weight, the bias $w_{0,i}^{(1)}$ , meaning that                                                                                                                                                                       |          |

|            | the contribution of the bias is $1 \cdot w_{0,i}^{(1)} = w_{0,i}^{(1)}$ .                                                                                                                                                                                               | 10       |

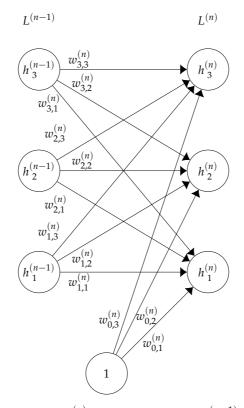

| 2.7        | A feedforward network with weights $w_{i,j}^{(n)}$ , $i, j = 1, 2, 3$ and biases $w_{0,j}^{(n)}$ shown for                                                                                                                                                              |          |

|            | each neuron.                                                                                                                                                                                                                                                            | 11       |

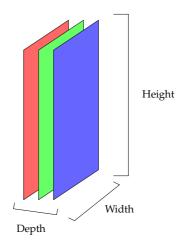

| 2.8        | A three-channel color image as seen by a convolutional neural network                                                                                                                                                                                                   | 12       |

| 2.9        | The receptive field of a convolutional network. The black grid is a single channel                                                                                                                                                                                      |          |

|            | of the input image, the red area shows the receptive field, in this case a $3 \times 3$ neighborhood.                                                                                                                                                                   | 12       |

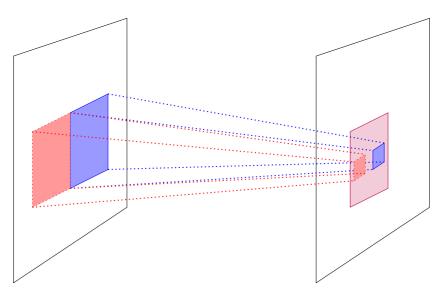

| 2 10       | Combination of local features in a later layer. The red and blue kernels in the left                                                                                                                                                                                    | 14       |

| 2.10       | layer process different areas of the image. The output of these separate operations                                                                                                                                                                                     |          |

|            | are both processed as part of the purple kernel in the right layer. For simplicity,                                                                                                                                                                                     |          |

| 0 1 1      | only one depth channel is shown.                                                                                                                                                                                                                                        | 13       |

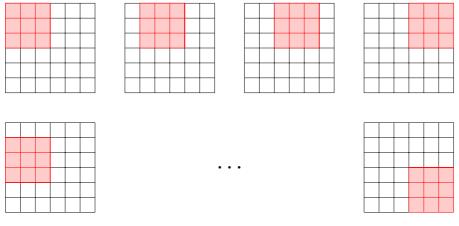

|            | Applying a $3 \times 3$ kernel to a $6 \times 6$ image with a stride of 1                                                                                                                                                                                               | 14<br>14 |

|            | An attempt at applying a $3 \times 3$ kernel to a $6 \times 6$ image with a stride of 3                                                                                                                                                                                 | 14       |

| 2.10       | of hyperparameters does not yield an integer when computing (2.21), meaning the                                                                                                                                                                                         |          |

|            | kernel will overstep. The part that falls outside the image is shown in brighter red.                                                                                                                                                                                   | 14       |

| 2.14       | A 3 $\times$ 3 kernel applied to a 5 $\times$ 5 image with stride 2. The 2 $\times$ 2 convolved feature                                                                                                                                                                 |          |

|            | is shown in the center. The colors indicate which application of the filter yielded                                                                                                                                                                                     |          |

|            | which part of the convolved feature.                                                                                                                                                                                                                                    | 15       |

| 2.15       | A $5 \times 5$ image with a zero padding of 1. The shaded area indicates the original                                                                                                                                                                                   | . –      |

|            | image whereas the cells with zeroes are added                                                                                                                                                                                                                           | 15       |

2.16 Convolving a padded  $5 \times 5$  image using a  $3 \times 3$  kernel applied with stride 2. The shaded gray area indicates the original image, the cells with zeroes are the padding. 16

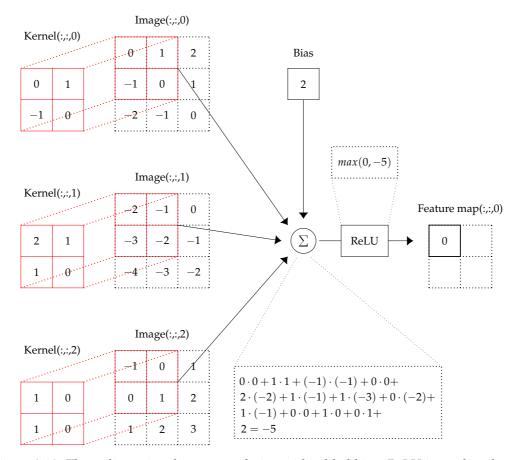

- 2.18 Three-dimensional cross-correlation with added bias. ReLU is used as the activation function. The notation A(:,:,n) signifies depth channel  $n \in \mathbb{Z}_0^+$ ,  $n \leq 2$  of order-three tensor A. The kernel is slid over the image and at each position the cross-correlation between the kernel and the image is computed. This is done in a per-channel fashion, meaning kernel depth channel 0 is applied to image depth channel 0, kernel channel 1 is applied to image channel 1 and so on. The sum of the contributions of the depth channels is added with the bias. This sum is passed through the ReLU activation function and the output placed in the feature map. .

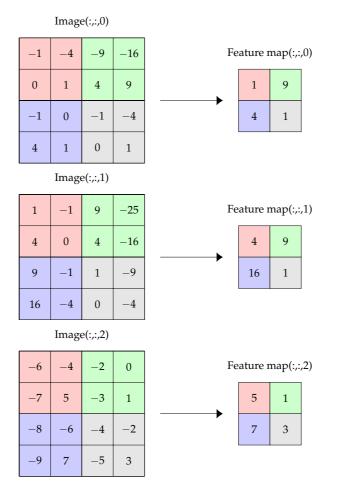

- 2.19 Max-pooling of an image with 3 depth channels using a  $2 \times 2$  kernel applied with a stride of 2. The max operation is applied independently to each depth channel and the result stored in the corresponding depth channel in the output. The colored cells in the output correspond to the  $2 \times 2$  area with the same color in the image. 19

18

30

2.20 Illustration of the approximate translation invariance of max-pooling. The upper image shows the result of applying max-pooling with a 3 × 1 kernel. In the lower image, the input has been shifted down one step. Despite the change in the input, large parts of the output remain the same.20

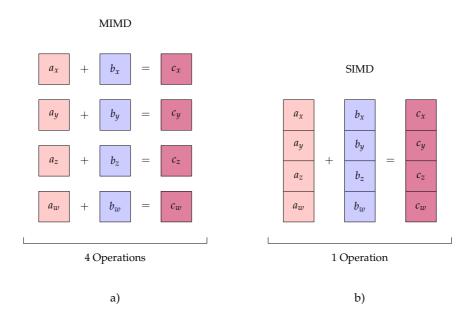

2.22 Parallel addition of two vectors, each consisting of four elements. a) A MIMD-based approach where each addition is performed by a separate thread. b) A SIMD-based approach, all additions performed in a single instruction by a single thread.22

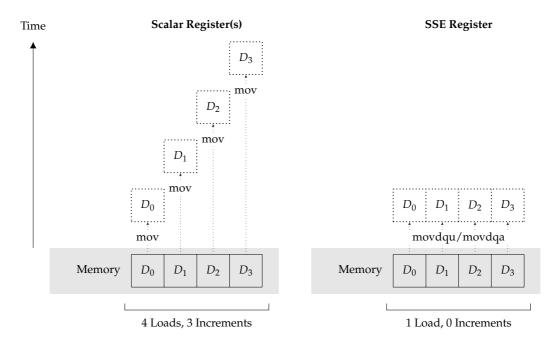

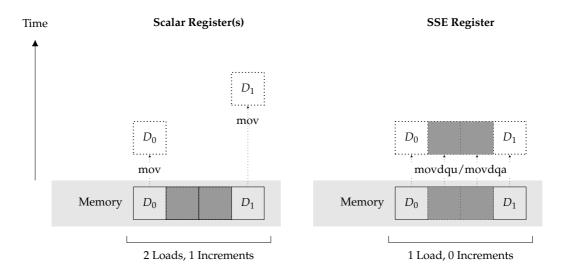

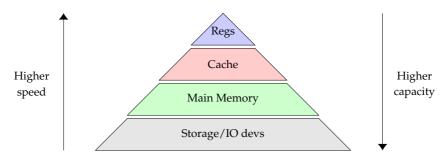

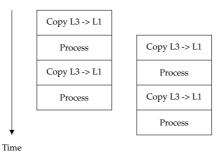

2.25 Memory access patterns for scalar and SSE registers where every third dword in memory is desired. Unused addresses and register lanes are shown in darker gray. The scalar registers operate by loading one dword at a time and then moving to the next. The SSE register loads 4 consecutive dwords at once but as the desired data elements are farther apart, two dwords are loaded in vain. 24 2.26 A typical memory hierarchy in a modern computer. 25 28 28 2.29 Conceptual illustration of asynchronous memory transfer from L3 to L1. . . . . . 29 2.30 Pipelining of the processing the values  $x_i$ , j = 0, ..., m, the instructions issued for each requiring the load-store, multiplier and add units. 30 2.31 An example of loop unrolling. a) Computing the sum of *n* elements using a regular loop. b) Computing the sum of n elements using a loop that has been manually

unrolled by a factor 2....

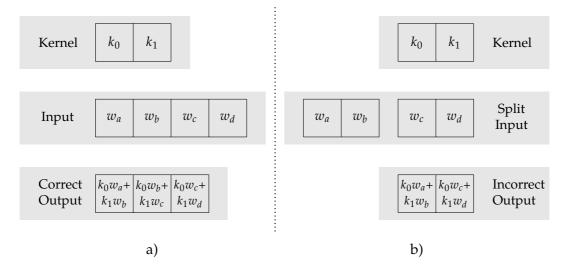

| 3.1<br>3.2 | Row-major storage of a two-dimensional array                                                                                                                | 32  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | incorrect.                                                                                                                                                  | 32  |

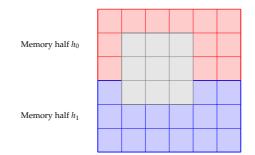

| 3.3        | A 3 $\times$ 3 filter kernel overlapping the two memory halves                                                                                              | 33  |

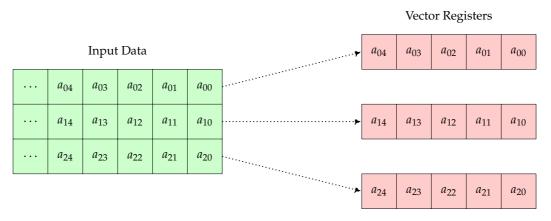

| 3.4        | Input data loaded into 5-lane vector registers                                                                                                              | 34  |

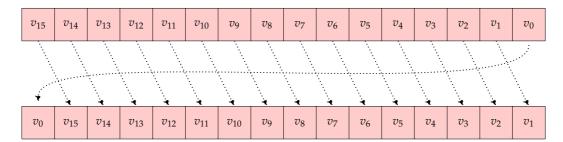

| 3.5        | Logical right rotation of a vector register.                                                                                                                | 35  |

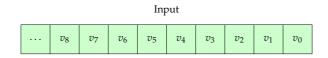

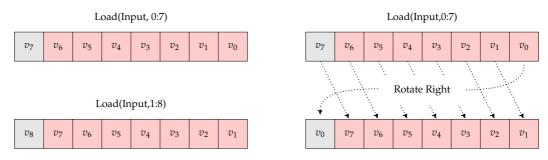

| 3.6        | Illustration of how packed rotations may be used to reduce the number of mem-                                                                               |     |

|            | ory loads. The two registers on the left are filled by issuing separate loads. The                                                                          |     |

|            | registers on the right are instead populated by a single load and a right rotation.                                                                         |     |

|            | The contents of the red lanes on the respective rows are the same                                                                                           | 35  |

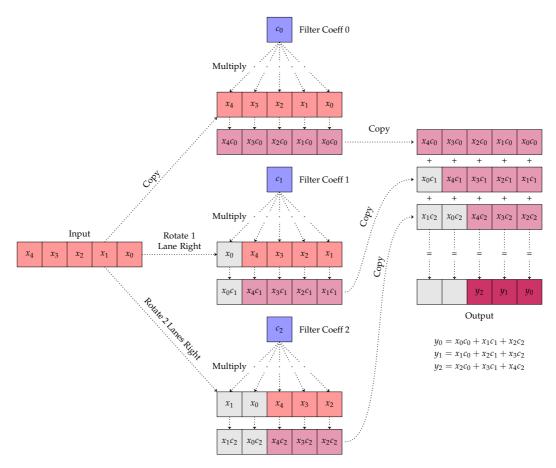

| 3.7        | Computing the cross-correlation of a one-dimensional signal and a $1 \times 3$ filter ker-                                                                  |     |

|            | nel using packed rotations, multiplications and additions. $x_i$ , $i = 0, 1,, 4$ is the                                                                    |     |

|            | <i>i</i> <sup>th</sup> sample of the input signal, $c_j$ , $j = 1, 2, 3$ the <i>j</i> <sup>th</sup> filter coefficient and $y_j$ the <i>j</i> <sup>th</sup> |     |

|            | component of the output. The content of gray lanes is unused.                                                                                               | 36  |

| 3.8        | Kernel position for the attempted $m - 1$ <sup>th</sup> application of a 1 × 3 kernel to the data                                                           | 50  |

| 5.0        | contained in an <i>m</i> -lane vector register. The kernel position is shown in blue. $\ldots$                                                              | 36  |

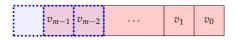

| 3.9        |                                                                                                                                                             | 30  |

|            | Packing of two vector registers.                                                                                                                            | 57  |

| 3.10       |                                                                                                                                                             |     |

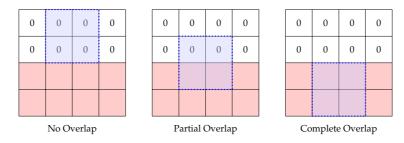

|            | an image. The red cells are part of the input and the cells with zeroes are part of                                                                         | •   |

|            | the padding. The position of the kernel is shown in blue.                                                                                                   | 38  |

| 3.11       | 1 1 0                                                                                                                                                       |     |

|            | emulated. The red cells are part of the input and the cells with zeroes part of the                                                                         |     |

|            | padding. The kernel position is shown in blue.                                                                                                              | 39  |

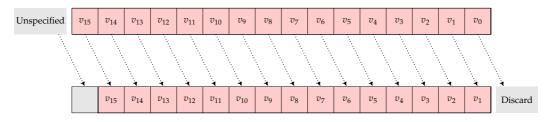

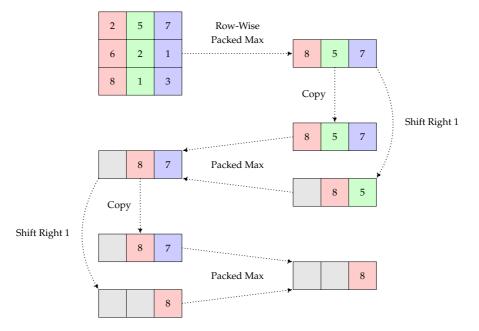

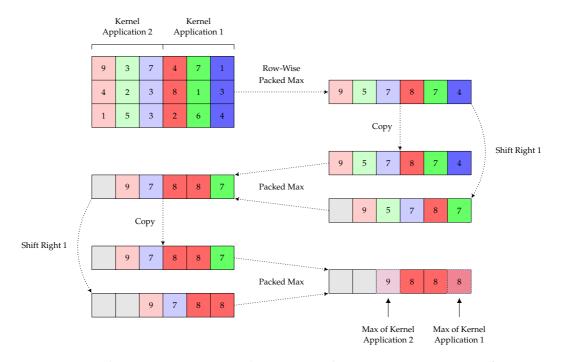

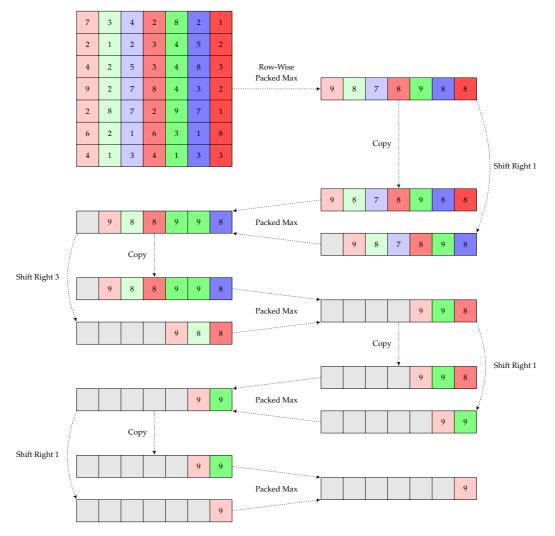

|            | Packed logical right shift of a vector register.                                                                                                            | 40  |

| 3.13       | Computing the maximum value of a $3 \times 3$ grid using logical right shifts and                                                                           |     |

|            | packed max operations. The content of gray lanes is unspecified.                                                                                            | 40  |

| 3.14       | A 6-lane vector register used to compute the respective maximums of two $3 \times 3$                                                                        |     |

|            | areas simultaneously.                                                                                                                                       | 41  |

| 3.15       | Computing the maximum value of a $7 \times 7$ grid. Each iteration of the horizontal                                                                        |     |

|            | max computation shifts the largest number of lanes possible in order to minimize                                                                            |     |

|            | the number of issued instructions.                                                                                                                          | 42  |

| 3.16       | Memory layout of a $35 \times 66$ weight matrix. Symbols in square brackets indicate                                                                        |     |

|            | row or column indices, remaining symbols are the memory offset of the particular                                                                            |     |

|            | element. The elements are arranged as they would be when viewing the weight                                                                                 |     |

|            | matrix written on paper. As an example, the 0 <sup>th</sup> element of row 1 of the matrix                                                                  |     |

|            | is stored as the 32 <sup>nd</sup> value in memory. The gray areas show how the matrix is                                                                    |     |

|            | arranged in memory blocks.                                                                                                                                  | 45  |

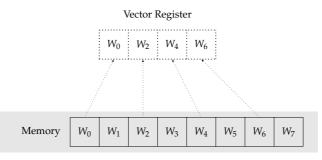

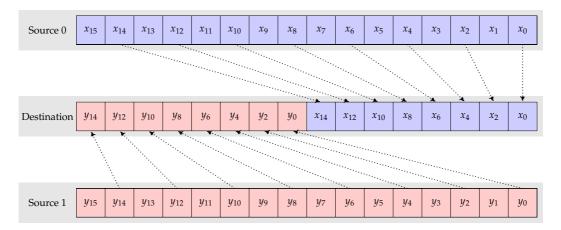

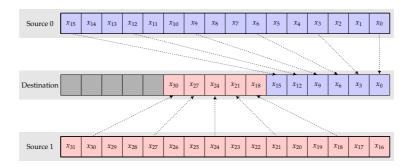

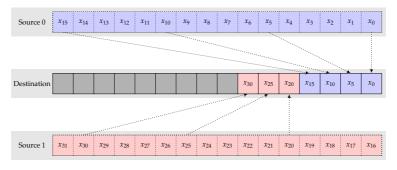

| 3.17       | Variable packing of two vector registers with period 3. The two source registers                                                                            |     |

|            | are treated as a single 32-lane register and every third lane is extracted and stored                                                                       |     |

|            | in the destination register. The values of gray lanes are unspecified                                                                                       | 47  |

| 3 18       | Variable packing of two vector registers with period 5.                                                                                                     | 47  |

| 5.10       | variable packing of two vector registers with period 5.                                                                                                     | -17 |

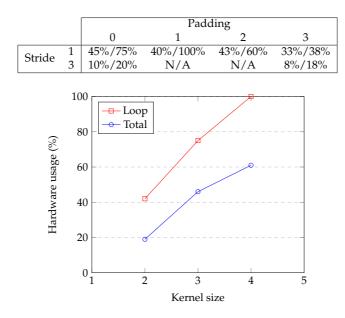

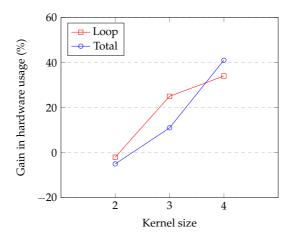

| 4.1        | Degree of usage, both in total and in the hardware loop, of the add and multiplier                                                                          |     |

|            | units as a function of kernel size. The convolution is computed using a square                                                                              |     |

|            | kernel, meaning a kernel size 2 signifies that a $2 \times 2$ kernel is used.                                                                               | 50  |

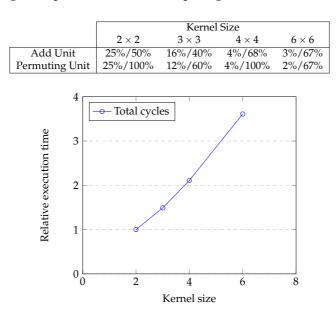

| 4.2        | Relative execution time of the entirety of the max-pooling implementation as a                                                                              |     |

|            | function of kernel size. Pooling with a $2 \times 2$ kernel is used as the baseline                                                                         | 51  |

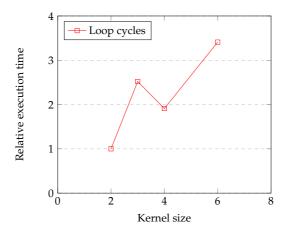

| 4.3        | Relative execution time of evaluating a single iteration of a hardware loop in the                                                                          | 51  |

| 1.0        | max-pooling implementation. The execution time is a function of kernel size.                                                                                |     |

|            | Pooling with a $2 \times 2$ kernel is used as the baseline                                                                                                  | 51  |

|            | rooms mara 2 ~ 2 kerter is used as the buseline                                                                                                             | 01  |

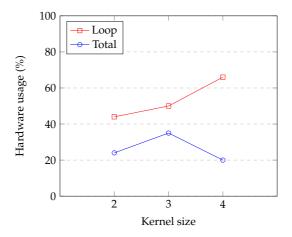

| 4.4 | Hardware usage when evaluating a convolutional layer without the improved      |    |

|-----|--------------------------------------------------------------------------------|----|

|     | pipelining                                                                     | 53 |

| 4.5 | The gain in hardware usage obtained by using the added pipelining instruction. | 53 |

## List of Tables

| 2.1 | Fundamental x86-64 data types with C counterparts                                     | 22 |

|-----|---------------------------------------------------------------------------------------|----|

| 2.2 | Total cache sizes of an AMD Ryzen 7 3700x processor.                                  | 26 |

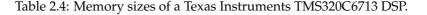

| 2.3 | Approximate access times to parts of the memory hierarchy of an Intel Xeon E5 v3.     | 27 |

| 2.4 | Memory sizes of a Texas Instruments TMS320C6713 DSP.                                  | 28 |

| 4.1 | Hardware usage when evaluating a convolutional layer using a $3 \times 3$ kernel with |    |

|     | different hyperparameters. The percentages are presented as total/loop usage.         |    |

|     | Results for hyperparameter choices for which the convolution is undefined are         |    |

|     | marked with $N/A$ .                                                                   | 50 |

| 4.2 | Hardware usage when evaluating a max-pooling layer using kernels of different         |    |

|     | sizes. The percentages are presented as total/loop usage                              | 51 |

| 4.3 | Hardware usage when evaluating a fully connected layer with different input and       |    |

|     | output sizes. The precentages are presented as total/loop usage                       | 52 |

| 4.4 |                                                                                       |    |

|     | pipelined multiplications, additions and rotations. Results for hyperparameter        |    |

|     | choices for which the convolution is undefined are marked with $N/A$ .                | 53 |

The use of machine learning on handheld devices has seen a significant increase over the past few years. It has become prominent enough that modern smartphones commonly include specialized chips for evaluating machine learning algorithms efficiently [1].

While having a clear use case, adding additional, advanced hardware components may run contrary to other desirable properties, affordability being perhaps chief among them. For this reason, MediaTek has expressed a desire to investigate the feasibility of evaluating machine learning algorithms on their digital signal processor (DSP). The DSP is an already integral part of the modem of most handheld devices. As such, using the DSP for evaluating the algorithms requires no additional hardware.

DSPs are microprocessors specialized in processing digital signals. They are of significant import in smartphones that regularly send and receive large amounts of data over mobile networks [2]. As such, DSPs are vital to the core functionality of most handheld devices whereas machine learning chips are more of an added luxury.

Given the tasks designated to them, DSPs feature a set of properties that differs from that of an ordinary CPU. As a result, they are apt at performing mathematical operations at high speed and with low power consumption [3]. Their high degree of specialization does, however, make them less suited to other tasks. One common limitation that stems from this specialization is that DSPs generally have access to significantly less memory [4] than CPUs.

Considering the large amount of data required by neural networks, it may prove difficult to implement them efficiently on a DSP. If, however, it were to be possible, it would allow for more affordable and powerful handheld devices.

#### 1.1 Motivation

DSPs are designed primarily with the processing of digital signals in mind. The benefits of features such as single-cycle memory access, vector instructions [5] and multiple-access memory [4] are, however, not limited to signal processing. This, in addition to DSPs in handheld devices being largely idle when not transferring data, makes it interesting to investigate how they may be used for solving other problems.

This thesis explores how a DSP may be employed to evaluate convolutional neural networks and whether it is a viable alternative to the specialized AI processing units used in handheld devices today. While it is unlikely that the efficiency of a dedicated AI chip is reached, it may still be possible to evaluate the algorithms on a sufficiently large DSP within an acceptable amount of time. This would in turn potentially allow for the possibility of forgoing the AI chips in handheld devices and thereby allowing them to be produced at a lower cost. Alternatively, the DSP could be used in tandem with the AI chips in order to increase throughput.

#### 1.2 Aim

The aim of the thesis is to investigate how the machine learning primitives convolutional, max-pooling and fully connected layers may be implemented on a DSP.

A successful approach should utilize inherent strengths of the DSP such as vector instructions and low memory latency. It should also solve issues that make the algorithms less suited to the architecture such as the memory restrictions inherent to the DSP. Additionally, potential changes to the instruction set of the processor that may improve performance should be suggested and evaluated.

#### 1.3 Research Questions

The thesis aims to answer the following research questions:

- How should the large amount of data required by neural networks be processed on a system where the size of both on- and off-chip memory is small?

- What machine learning primitives lend themselves well to vector processing and how, if at all, may the processor be altered to make the fit better?

#### 1.4 Method at a Glance

In order to provide a foundation solid enough for answering the research questions, the thesis proposes algorithms for evaluating convolutional, max-pooling and fully connected layers. The algorithms proposed have been honed by gradually altering them such that they make better use of the available hardware in the DSP provided by MediaTek.

The thesis details ways of managing on- and off-chip memory such that excessive data transfers are avoided and the latency of required data transfers is hidden. It also suggests ways of restructuring certain data in order to increase throughput of the proposed algorithms.

Changes proposed for the processor include two new instructions designed with the implementation of the algorithms in mind. These allow for improved pipelining and packing of data in vector registers using a variable period, respectively. In order to measure the impact of the proposed instructions, they were temporarily added to the instruction set of the DSP.

#### 1.5 Delimitations

For the sake of time-constraints, the thesis considers only convolutional, max-pooling and fully connected layers. The primitives are considered as fully separate rather than as part of an actual network of a particular configuration. As such, the results should be applicable to any convolutional neural network constructed from the primitives in question.

As the aim of the thesis is to investigate the feasibility of running neural networks on a DSP, it is more concerned with the fundamental processes involved than achieving meaningful output of the network. This means that designing a neural network that successfully performs a given task is of less interest. By extension, tuning of network parameters through learning algorithms is left out entirely. Instead, the intent is to investigate different implementations of the chosen primitives and adapt them to the DSP. The scope of the thesis is limited to work only with the DSP designed and provided by MediaTek and may rely on solutions that are unique to its instruction set. As the latter is not publicly available, any such solution will, when applicable, be described using similar concepts available on more common architectures.

While proposing potential changes that would allow the DSP to more efficiently evaluate the primitives is within the scope of the thesis, these are restricted to deal only with the instruction set. Aspects beyond this such as numeric representations and memory sizes are considered fixed. Furthermore, potential issues that arise due to floating point rounding are not considered.

This chapter presents the theoretical foundation of the thesis. It starts by establishing a mathematical basis and subsequently delves into the inner workings of neural networks. Aspects central to high performance computing such as data parallelism and memory considerations are also presented. The chapter concludes by exploring digital signal processors.

#### 2.1 Mathematical Concepts

The large number of machine learning frameworks available has made it possible to employ convolutional neural networks without much concern for the mathematics behind them. Implementing them, on the other hand, requires an understanding of the underlying primitives. This section begins by describing tensors, a concept used frequently in the context of neural networks. It continues by presenting convolution and cross-correlation, two fundamental building blocks of convolutional neural networks.

#### 2.1.1 Tensors

Tensors are a mathematical generalization of vectors. A tensor has a magnitude and an arbitrary number of directions. The number of these directions for a particular tensor is referred to as its order. By this definition, a tensor of order 0 has a magnitude and no direction associated with it. In other words, a tensor of order 0 is a scalar. Tensors of order 1 have a magnitude and a single direction, meaning they are vectors [6].

Higher order tensors are less intuitive. A tensor of order 2, a so-called dyad, is constructed by the dyad product of two vectors. Given two vectors  $\mathbf{u} = u_1\mathbf{e_1} + u_2\mathbf{e_2} + u_3\mathbf{e_3}$  and  $\mathbf{v} = v_1\mathbf{e_1} + v_2\mathbf{e_2} + v_3\mathbf{e_3}$ , the dyad product  $\mathbf{uv}$  is given by

$$\mathbf{u}\mathbf{v} = \sum_{i=1}^{3} \sum_{j=1}^{3} u_i v_j \mathbf{e}_i \mathbf{e}_j$$

(2.1)

where  $\mathbf{e}_1$ ,  $\mathbf{e}_2$  and  $\mathbf{e}_3$  are linearly independent unit vectors [6].

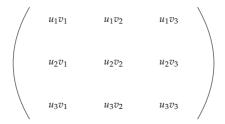

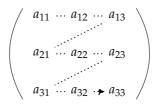

Second order tensors have a single magnitude and two directions. By allowing the subscripts i and j in (2.1) to denote row and column, respectively, the scalar components of the dyad can be arranged in a matrix [6] as shown in Fig. 2.1.

Figure 2.1: Scalar components of a second order tensor visualized in a matrix-like structure.

Order three tensors are defined by the triad product **uvw** [6] where **u** and **v** are defined as above and  $\mathbf{w} = w_1\mathbf{e}_1 + w_2\mathbf{e}_2 + w_3\mathbf{e}_3$ . The triad product is computed in a similar way to its dyad counterpart but sums over an additional dimension. More specifically,

$$\mathbf{uvw} = \sum_{i=1}^{3} \sum_{j=1}^{3} \sum_{k=1}^{3} u_i v_j w_k \mathbf{e}_i \mathbf{e}_j \mathbf{e}_k$$

(2.2)

computes the triad product **uvw** [6].

Tensors of an arbitrary order  $n \in \mathbb{Z}^+$ , n > 3 are defined analogously to their lower order counterparts and, similarly, have *n* directions and  $3^n$  components [6].

In computer science, the term tensor is generally used as a synonym for the scalar components of the mathematical tensor. As such, they are no more than multi-dimensional arrays and are used in order to generalize matrices beyond two dimensions [7]. Additionally, the restriction of the tensor containing  $3^n$  components is lifted. As a consequence, a tensor of order three may be used to reference any arbitrary, three-dimensional array [8].

When used in the thesis, unless otherwise stated, the term tensor refers to the more liberal computer science interpretation.

#### 2.1.2 Convolution

Convolution is a mathematical operation that given two functions produces a third [9]. For two continuous signals f(t) and g(t),

$$h(t) = (f * g)(t) = \int_{-\infty}^{\infty} f(\tau)g(t - \tau)d\tau$$

(2.3)

computes their convolution h(t) [10].

In fields such as image processing, machine learning and signal processing, the data processed is discrete. As a result, researchers in these fields typically present convolution as a summation over discrete points. Considering two discrete functions f'(n) and g'(n),

$$h'(n) = (f' * g')(n) = \sum_{i=-\infty}^{\infty} f'(i)g'(n-i)$$

(2.4)

yields their discrete convolution h'(n). As can be seen, discrete convolution computes the inner products of local neighborhoods of signal samples and a time-reversed kernel [10]. The fact that the kernel is time-reversed is indicated by the sign preceding *i* in g'(n - i). In (2.4), the input signal is g'(n), the kernel f'(n) and the convolution is performed over the neighborhood of the  $n^{\text{th}}$  sample.

In practical applications such as image processing and machine learning, the convolution kernel is defined to be non-zero over a finite number of data points. As a consequence, the infinite summation interval can be reduced to comprise a finite set of elements [8].

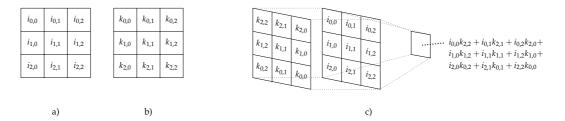

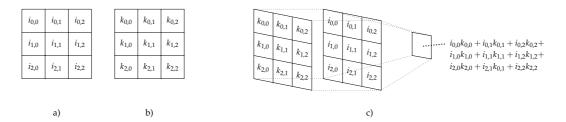

Figure 2.2: Application of a  $3 \times 3$  convolution filter to a  $3 \times 3$  image. a) The input image. b) The filter kernel. c) Application of the filter kernel to the input image in order to produce a convolved feature.

Convolution may be extended to higher dimensions. The discrete convolution of a function  $g^{2d}(n_x, n_y)$  and a two-dimensional kernel  $f^{2d}(n_x, n_y)$  is computed using

$$h^{2d}(n_x, n_y) = (f^{2d} * g^{2d})(n_x, n_y) = \sum_i \sum_j f^{2d}(i, j) g^{2d}(n_x - i, n_y - j)$$

(2.5)

where  $h^{2d}(n_x, n_y)$  is the so-called convolved feature [8] and  $n_x$  and  $n_y$  denote indices for column and row in the image, respectively. Additionally, the boundaries for *i* and *j* are left out as they are of limited importance in practice. Fig. 2.2 shows how the two-dimensional filter kernel is reversed when convolving an image.

Example usages of two-dimensional convolution include noise reduction and edge detection in image processing [10]. It is, however, limited to greyscale images. In order to convolve color images, three-dimensional convolution is required. For two given functions  $f^{3d}(n_x, n_y, n_z)$  and  $g^{3d}(n_x, n_y, n_z)$ , their convolved feature  $h^{3d}(n_x, n_y, n_z)$  is computed as

$$h^{3d} = (f^{3d} * g^{3d}) = \sum_{i} \sum_{j} \sum_{k} f^{3d}(i, j, k) g^{3d}(n_x - i, n_y - j, n_z - k).$$

(2.6)

Here, the fact that  $h^{3d}$  and  $(f^{3d} * g^{3d})$  are both functions of  $n_x$ ,  $n_y$  and  $n_z$  is left out for notational convenience.

#### 2.1.2.1 Fourier Transform-Based Convolution

Whereas convolution may be computed by simply applying the mathematical definition, other methods have been explored. One such method relies on convolution in the time domain transforming to multiplication in the frequency domain. Instead of convolving the input in time domain, both the signal and the kernel are transformed using a fast Fourier transform. This is followed by a multiplication and an inverse Fourier transform, yielding the convolved feature of the input [11]. More specifically, the Fourier transform-based convolution of two functions f and g is computed using

$$(f * g)(t) = \mathcal{F}^{-1}(\mathcal{F}(f(t))\mathcal{F}(g(t)))$$

$$(2.7)$$

where  $\mathcal{F}$  and  $\mathcal{F}^{-1}$  denote Fourier transform and inverse Fourier transform, respectively.

In terms of performance, Fourier transform-based convolution may outperform direct convolution under certain conditions. Assuming an  $n \times n$  input image and a  $k \times k$  filter kernel, direct, two-dimensional convolution requires  $(n - k + 1)^2 k^2 \in O(n^2 k^2)$  multiplications. The number of multiplications in Fourier transform-based convolution is  $cn^2\log(n) + 4n^2 \in O(n^2\log(n))$  for some  $c \in \mathbb{R}$  [11].

#### 2.1.2.2 Separable Convolution

Another common convolution approach is so-called separable convolution. The technique separates the filter kernel into two separate components, one vertical and one horizontal. The

actual convolution is performed over two steps. In the first step, the input is convolved with the first of the separated components, producing an intermediary signal. This intermediary is then convolved with the second separated component, producing the convolved feature [3].

A kernel being separable means that it can be decomposed into a horizontal and a vertical part that when convolved with each other produce the original kernel [3]. Using the horizontal Sobel operator as an example, this can be summarized as

$$\begin{bmatrix} 1 & 0 & -1 \\ 2 & 0 & -2 \\ 1 & 0 & -1 \end{bmatrix} = \begin{bmatrix} 1 \\ 2 \\ 1 \end{bmatrix} * \begin{bmatrix} -1 & 0 & 1 \end{bmatrix}$$

(2.8)

where the vectors in the right-hand side are the separated components and \* is the convolution operator.

Separable two-dimensional convolution of an  $n \times n$  size image with a  $k \times k$  kernel is computed in time  $O(n^2k)$  [3]. As such, it is strictly less computationally expensive than direct convolution. The difficulty with the approach lies in ascertaining that a particular convolution kernel is separable.

Whether a two-dimensional kernel is separable can be determined by computing the rank of the corresponding matrix. If the matrix is of rank 1, meaning all but one of its columns are linearly dependent, the kernel is separable [12]. Separability of tensors of arbitrary order is instead determined via the so-called nuclear norm. As with the rank of a matrix, a tensor is separable if and only if its nuclear norm is 1 [13]. Whereas matrix rank can be computed in polynomial time using Gaussian elimination [14], determining the nuclear norm of even an order-three tensor is NP-hard [15].

#### 2.1.3 Cross-Correlation

The cross-correlation c(t) of two continuous functions is given by

$$c(t) = (f \star g)(t) = \int_{-\infty}^{\infty} f(\tau)g(t+\tau)d\tau$$

(2.9)

where f(t) is the filter kernel and g(t) the input signal [16]. Comparing this to (2.3), it is evident that the only difference between convolution and cross-correlation is the sign preceding the  $\tau$  in the second term of the integral [8].

Cross-correlation can be both discretized and extended to higher dimensions in the same way as convolution [8]. Consequently, given two discrete functions  $f^{3d}(n_x, n_y, n_z)$  and  $g^{3d}(n_x, n_y, n_z)$ , their cross-correlation  $c^{3d}(n_x, n_y, n_z)$  is given by

$$c^{3d} = (f^{3d} \star g^{3d}) = \sum_{i} \sum_{j} \sum_{k} f^{3d}(i, j, k) g^{3d}(n_x + i, n_y + j, n_z + k).$$

(2.10)

Like (2.6), (2.10) does not explicitly specify that both  $c^{3d}$  and  $(f^{3d} \star g^{3d})$  are functions of  $n_x$ ,  $n_y$  and  $n_z$  for notational convenience. As can be seen, the only difference between (2.6) and (2.10) is that the subtractions in (2.6) are replaced by additions in (2.10).

Conceptually, replacing the subtractions with additions means that the filter kernel is no longer spatially reversed when computing the inner products [8]. Fig. 2.3 illustrates this. The main difference between convolution and cross-correlation in terms of mathematical properties is that the former is commutative whereas the latter is not [8].

#### 2.2 Neural Networks

Neural networks are among the most popular machine learning models used today [8]. They are commonly visualized as directed acyclic graphs consisting of an input layer, one or more

Figure 2.3: Application of a  $3 \times 3$  cross-correlation filter to a  $3 \times 3$  image. a) The input image. b) The filter kernel. c) Application of the filter kernel to the input image and the resulting output.

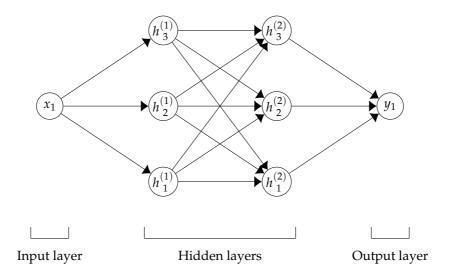

Figure 2.4: A feedforward neural network with a single input, a single output and two hidden layers, each of which consisting of three neurons. The superscripts of the hidden neurons indicate to which layer they belong and the subscripts their index in said layer. Neither weights nor biases are shown.

hidden layers and an output layer. Formally, the type of network that is usually shown is called a feedforward neural network [8]. Fig. 2.4 shows such a network containing two hidden layers.

As can be seen in Fig. 2.4, each neuron except for the input  $x_1$  is connected to all neurons in the preceding layer. Generally, when each neuron in the  $n^{\text{th}}$  layer  $L^{(n)}$  is connected to all the neurons in its input layer  $L^{(n-1)}$ ,  $L^{(n)}$  is said to be fully connected. A fundamental property of feedforward networks is that all layers but the input layer fulfill this property [8].

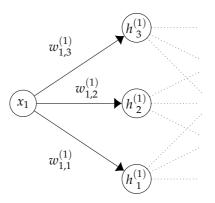

Fig. 2.4 omits a few important aspects, namely weights, biases and hidden units. The weights of a feedforward neural network correspond to the edges of the graph representation [17]. Fig. 2.5 shows the input and first hidden layer of the network in Fig. 2.4 with the weights added. The weights perform a per-neuron scaling of the input according to

$$a_{j}^{(n)} = \sum_{i=1}^{d} w_{i,j}^{(n)} h_{i}^{(n-1)}$$

(2.11)

where  $a_j^{(n)} \in \mathbb{R}$  is a linear combination of the inputs of neuron *j* in layer  $L^{(n)}$ . The upper limit  $d \in \mathbb{Z}^+$  is the number of inputs of said layer and the weight  $w_{i,j}^{(n)} \in \mathbb{R}$  is associated with the

Figure 2.5: Input and first hidden layer of the network shown in Fig. 2.4 with added weights. The superscripts of the weights denote which layer the neuron at the end of the edge belongs to. The subscripts indicate which neurons in the two layers are connected.

edge connecting neuron *i* in layer  $L^{(n-1)}$  with neuron *j* in layer  $L^{(n)}$ . The so-called activation  $h_i^{(n-1)} \in \mathbb{R}$  of the *i*<sup>th</sup> neuron in layer  $L^{(n-1)}$  serves as the *i*<sup>th</sup> input to layer  $L^{(n)}$  [17]. For the part of the network that is shown in Fig. 2.5, there is a single input  $x_1$ , meaning

For the part of the network that is shown in Fig. 2.5, there is a single input  $x_1$ , meaning d = 1 and the summation in (2.11) is performed over a single element. Using this, the linear combinations  $a_1^{(1)}$ ,  $a_2^{(1)}$  and  $a_3^{(1)}$  corresponding to neurons  $h_1^{(1)}$ ,  $h_2^{(1)}$  and  $h_3^{(1)}$  are given by

$$a_{1}^{(1)} = w_{1,1}^{(1)} x_{1}, \tag{2.12}$$

$$a_{2}^{(1)} = w_{1,2}^{(1)} x_{1}, \tag{2.13}$$

and

$$a_{3}^{(1)} = w_{1,3}^{(1)} x_{1} \tag{2.14}$$

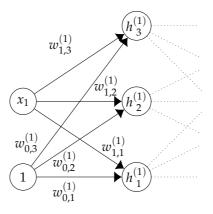

respectively. As can be seen, the linear combinations are obtained by scaling the input of the respective neurons with its corresponding weight. This model can be further refined by adding a bias for each neuron [17]. The result of adding a bias for each neuron in Fig. 2.5 is shown in Fig. 2.6.

With the added bias terms  $w_{0,j}^{(1)} \in \mathbb{R}$ , the linear combination  $a_j^{(1)} \in \mathbb{R}$ , j = 1, 2, 3 of neuron  $h_j^{(1)}$  in Fig. 2.6 is computed via

$$u_{j}^{(1)} = w_{1,j}^{(1)} x_{i} + w_{0,j}^{(1)}.$$

(2.15)

This is generalized to compute the linear combination  $a_j^{(n)}$  corresponding to the  $j^{\text{th}}$  neuron in layer  $L^{(n)}$  using

$$a_{j}^{(n)} = \sum_{i=1}^{d} w_{i,j}^{(n)} h_{i}^{(n-1)} + w_{0,j}^{(n)}$$

(2.16)

where *d* is the number of layer inputs and  $h_i^{(n-1)}$  is the activation of the *i*<sup>th</sup> neuron of layer  $L^{(n-1)}$ .

The activation  $h_j^{(n)}$  of the *j*<sup>th</sup> neuron in layer  $L^{(n)}$  is produced by feeding its corresponding linear combination  $a_j^{(n)}$  through a so-called activation function. The latter is a non-linear, piecewise differentiable function. Common choices include the sigmoid [17] defined as

$$\sigma(x) = \frac{1}{1 + e^x} \tag{2.17}$$

Figure 2.6: Fig. 2.5 with a bias  $w_{0,j}^{(1)}$  added for each hidden neuron  $h_j^{(1)}$ , j = 1, 2, 3. The biases are visualized as weights for edges between neurons in the hidden layer and an input neuron with value 1. When evaluating the network, the contribution of this input neuron is its value, 1, multiplied with its weight, the bias  $w_{0,j}^{(1)}$ , meaning that the contribution of the bias is  $1 \cdot w_{0,j}^{(1)} = w_{0,j}^{(1)}$ .

and the rectified linear unit, known as the ReLU [8], given by

$$\operatorname{ReLU}(x) = \max(0, x). \tag{2.18}$$

The output  $h_j^{(n)}$  of the activation function for the  $j^{\text{th}}$  hidden neuron in the  $n^{\text{th}}$  layer  $L^{(n)}$  is used as input for the neurons in the subsequent layer  $L^{(n+1)}$  and the same procedure is repeated [17]. In other words, the activation  $h_j^{(n)} \in \mathbb{R}$  of neuron j in layer  $L^{(n)}$  is computed using

$$h_{j}^{(n)} = \Phi\left(a_{j}^{(n)}\right) = \Phi\left(\sum_{i=1}^{d} w_{i,j}^{(n)} h_{j}^{(n-1)} + w_{0,j}^{(n)}\right)$$

(2.19)

where  $\Phi : \mathbb{R} \to \mathbb{R}$  is a general activation function and  $w_{i,j}^{(n)}$  is the weight applied to the *i*<sup>th</sup> layer input  $h_i^{(n-1)}$ . The term  $w_{0,j}^{(n)}$  is the bias corresponding to the *j*<sup>th</sup> neuron in layer  $L^{(n)}$  and *d* is the number of layer inputs.

When the data has propagated through the entire network and reached the output neuron, the input of the latter is transformed to a meaningful output. This meaningful output may, as an example, be a vector of class scores. The transformation is performed using yet another activation function [17]. This activation function is usually different from the ones used in earlier layers and is chosen according to what fits the particular task of the network [18].

Fig. 2.7 shows a simple feedforward network complete with weights and biases for each neuron. Choosing the ReLU and sigmoid functions as the activation functions for the hidden and output layers respectively, the entire forward pass of the network in Fig. 2.7 is given by

$$y_1 = \sigma \left( \sum_{j=1}^2 w_{j,1}^{(2)} \operatorname{ReLU} \left( x_1 w_{1,j}^{(1)} + w_{0,j}^{(1)} \right) + w_{0,1}^{(2)} \right).$$

(2.20)

Here, the input  $x_1 \in \mathbb{R}$  is first scaled with a weight  $w_{1,j}^{(1)} \in \mathbb{R}$  in the first layer and added with the corresponding bias  $w_{0,j}^{(1)} \in \mathbb{R}$ . The sum is passed through the ReLU activation function. This is done for each neuron  $h_j^{(1)}$  in the hidden layer, hence the summation over *j*. The computed values, the so-called output unit activations, effectively serve as the input for the

Figure 2.7: A feedforward network with weights  $w_{i,j}^{(n)}$ , i, j = 1, 2, 3 and biases  $w_{0,j}^{(n)}$  shown for each neuron.

output layer. As such, they are scaled with their corresponding weights  $w_{j,1}^{(2)} \in \mathbb{R}$ . The sum of the scaled output unit activations is then added with the output bias  $w_{0,1}^{(2)} \in \mathbb{R}$  and, finally, this sum is passed through the sigmoid activation function to produce the output  $y_1 \in \mathbb{R}$  of the network.

#### 2.2.1 Neural Network Pruning

As the applications of neural networks become increasingly complex, so do the networks themselves [19]. Larger networks require a larger number of computations to evaluate. This makes using neural networks on resource-constrained systems such as embedded devices difficult [20].

Neural network pruning is an umbrella term for different techniques used to reduce the computational complexity of neural networks [21]. This is usually achieved by removing individual weights of the network based on certain criteria. Which weights to remove is determined by including a measure of the computational complexity in the cost function used when training the network [19].

As pruning reduces the total number of weights of the network, it may affect how well said network manages the tasks designated to it [19]. While it might initially seem as though reducing the number of weights in the network would lead to less accurate results, this is not necessarily the case. Instead, reducing the number of weights can improve how well a network generalizes to arbitrary inputs. Pruning should, however, be used with moderation as removing too many weights will result in the network no longer being able to approximate the data [19].

#### 2.3 Convolutional Neural Networks

While feedforward networks are powerful, their high degree of connectivity makes them less suited to certain tasks. Connecting each neuron in a layer to each neuron in the prior means that all inputs are considered at each position, something that is not necessarily desirable. A common scenario when this is less suitable is when working with images as pixels close to each other tend to have a higher correlation than pixels farther apart [17]. For these types of input, convolutional neural networks are usually preferred instead.

As image processing is the perhaps most common application of convolutional networks, this section assumes the network input is a three-channel color image. The principles do, however, apply to any three-dimensional type of data.

Whereas feedforward networks accept an arbitrary number of scalar inputs, convolutional networks are usually considered taking a single order-three tensor. When working with im-

Figure 2.8: A three-channel color image as seen by a convolutional neural network.

Figure 2.9: The receptive field of a convolutional network. The black grid is a single channel of the input image, the red area shows the receptive field, in this case a  $3 \times 3$  neighborhood.

ages, the conceptual width and height of the tensor correspond to the width and height of the input image. The three depth channels of the tensor represent the red, green and blue channels, respectively [22]. These depth channels are commonly referred to as feature maps [17]. A possible input of a convolutional network is shown in Fig. 2.8. The feature maps of the input correspond to the red, green and blue planes in the illustration.

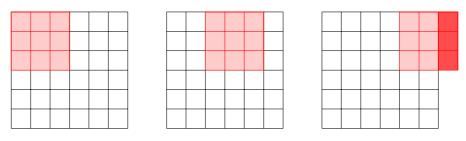

A key concept of convolutional networks is that they work with so-called local receptive fields [17], meaning that only part of the input image is processed at a time. In practice, this is realized by applying a smaller kernel to the image over a series of steps. Fig. 2.9 shows the receptive field of a network using a  $3 \times 3$  kernel. The spatial locality of the kernel allows for extracting local features from subregions of the image. These local features may in subsequent layers be combined with others, ultimately yielding information about the image as a whole [17]. Fig. 2.10 shows how two subregions processed separately may in a later layer both come to influence the result.

As the input is processed in smaller parts at a time, convolutional networks allow for what is called weight sharing. This means that rather than storing a different weight for each pair of connected neurons as done in feedforward networks, a single, smaller kernel suffices. This kernel consists of the layer weights and is typically shared for the entire layer [17]. For large neural networks, this weight sharing may allow for significantly reduced memory usage. Additionally, it contributes to the so-called translation invariance of the network [23].

Sharing the kernel of weights among all neurons in a layer means that the evaluation of the activation of a neuron is equivalent to convolving its input with the kernel [17]. This is, however, rarely how convolutional layers in convolutional networks are implemented. Instead, a large number of machine learning frameworks prefer using cross-correlation. This yields the same observable behavior of the network despite the mathematical result being different [8].

Figure 2.10: Combination of local features in a later layer. The red and blue kernels in the left layer process different areas of the image. The output of these separate operations are both processed as part of the purple kernel in the right layer. For simplicity, only one depth channel is shown.

The activations produced by the convolutional layers are, like in feedforward networks, fed through a non-linear activation function before they are used as input for the subsequent layer. The ReLU is a common choice of activation function here as well [8].

In addition to convolutional layers with added non-linearities, downsampling is an important property employed by convolutional networks. The downsampling is more commonly referred to as pooling and it replaces an area of its input with a summary statistic of said area [8]. A common choice of summary is to simply choose the maximum intensity of the area. This particular version of pooling is referred to as max-pooling [22].

In some literature, the convolution, activation and pooling are considered to constitute a single, three-part layer of the network. Others choose to treat pooling as a separate layer. In this thesis, the latter is preferred as notable convolutional networks such as the VGG16 consist of several convolutional layers with no pooling layers in-between [24].

The final primitive to be considered in the thesis is the fully connected layer. This layer is reminiscent of the ones in feedforward networks in the sense that each neuron is connected to all neurons in its input layer [22]. As fully connected layers are both compute- and memory-intensive, they are generally used sparingly and among the last layers of a network. Examples of this include the VGG16 [24] and AlexNet [25].

#### 2.3.1 Hyperparameters

Processing the image in parts introduces a need for the so-called hyperparameters stride, padding and output depth. Stride refers to with what interval the kernel is applied to the image whereas padding is a means of preserving information at the borders of the image [22]. The output depth determines the number of depth channels in the subsequent layer [26].

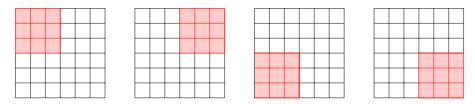

The stride controls the overlap of the kernels and, by extension, the size of the output [22]. Fig. 2.11 shows the procedure of applying a  $3 \times 3$  kernel to a  $6 \times 6$  single-channel image with a stride of 1. At each stage, the kernel is moved a single step to the right. When the end of a row is reached, the kernel is moved one step down to the next. In each step, a single value is produced for a total of 16.

Fig. 2.12 shows the result of applying a  $3 \times 3$  kernel to a  $6 \times 6$  single-channel image with a stride of 3. Here, the kernel is moved 3 pixels along each row at every step. When the end

Figure 2.11: Applying a  $3 \times 3$  kernel to a  $6 \times 6$  image with a stride of 1.

Figure 2.12: Applying  $3 \times 3$  kernel to a  $6 \times 6$  image with a stride of 3.

Figure 2.13: An attempt at applying a  $3 \times 3$  kernel to a  $6 \times 6$  image with a stride of 2. The choice of hyperparameters does not yield an integer when computing (2.21), meaning the kernel will overstep. The part that falls outside the image is shown in brighter red.

of a row is reached, the kernel is moved 3 rows down. Since the kernel is applied at only 4 positions, the filtering produces a total of 4 values. As is evident, a larger stride results in a smaller output. Assuming a  $k \times k$  size kernel, an  $n \times n$  image and a stride  $s \in \mathbb{Z}^+$ ,

$$o = \frac{n-k}{s} + 1 \tag{2.21}$$

computes the size  $o \in \mathbb{Z}^+$  of the square output [22].

As the width and height of an image are expressed in pixels, it can be observed that the fraction in (2.21) must yield an integer. This means that the stride *s* should be chosen such that it divides n - k. The result of not respecting this constraint is shown in Fig. 2.13.

As seen in Fig. 2.11, kernel applications may cause the spatial size of the output to be smaller than that of the input. This is not always desirable, especially not when several convolutional layers using the same size filter kernel are used in direct succession. Fig. 2.14 aims to demonstrate this issue more clearly. It shows the result of convolving a  $5 \times 5$  image with a  $3 \times 3$  kernel using a stride of 2. As can be seen, the convolved feature has the dimensions  $2 \times 2$ , meaning there is no way to apply the same  $3 \times 3$  filter kernel to it.

Figure 2.14: A  $3 \times 3$  kernel applied to a  $5 \times 5$  image with stride 2. The  $2 \times 2$  convolved feature is shown in the center. The colors indicate which application of the filter yielded which part of the convolved feature.

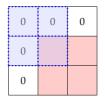

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|

| 0 |   |   |   |   |   | 0 |

| 0 |   |   |   |   |   | 0 |

| 0 |   |   |   |   |   | 0 |

| 0 |   |   |   |   |   | 0 |

| 0 |   |   |   |   |   | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Figure 2.15: A  $5 \times 5$  image with a zero padding of 1. The shaded area indicates the original image whereas the cells with zeroes are added.

The downsizing that occurs during a filter application can be regarded as an unwanted loss of information. The most common way of addressing the issue is by zero-padding the input. This means that extra rows and columns containing all zeroes are added to the input image [22]. An example of this can be seen in Fig. 2.15 where a  $5 \times 5$  image with a padding of 1 is shown. While zeroes are the most common form of padding, alternative approaches such as repeating [27] or using mean values of [28] edge pixels have been proposed.

Padding allows for controlling the spatial size of the convolved feature [26]. Fig. 2.16 shows how using the same image, kernel and stride as in Fig. 2.14 but with a zero padding of 1 impacts the convolved feature. Instead of the output having dimensions  $2 \times 2$  as in Fig. 2.14, the convolved feature in Fig. 2.16 is  $3 \times 3$ . The size of the output can be computed by including the padding in (2.21). With *k* and *s* again corresponding to the kernel size and stride, respectively,

$$o = \frac{n - k + 2p}{s} + 1 \tag{2.22}$$

computes the size *o* of the convolved feature obtained when convolving an  $n \times n$  input image with padding  $p \in \mathbb{Z}_0^+$  [22].

Figure 2.16: Convolving a padded  $5 \times 5$  image using a  $3 \times 3$  kernel applied with stride 2. The shaded gray area indicates the original image, the cells with zeroes are the padding.

Whereas padding allows for manipulating the width and height of the output, it does not change the output depth. This is instead controlled by the number of neurons used to look at the same area of the image [26]. In practice, this equates to applying several kernels to the same position of the image and allowing each to contribute to a separate depth channel [29]. This is illustrated in Fig. 2.17.

#### 2.3.2 Convolutional Layer

The convolutional layers are referred to as the feature detectors of a convolutional network [26]. As the appellation implies, they are used to identify feature representations in the input [30]. What these features are depends on how the network is trained, but common examples are edges and other intensity changes in the image [26].

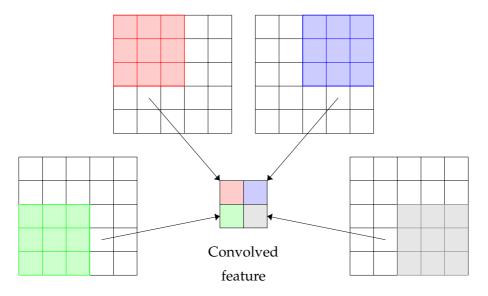

When working with three-channel color images, the main operation performed by the convolutional layers is a three-dimensional convolution [29] or, in practice, cross-correlation [8]. Despite the mathematical differences, this section does not distinguish between the two as they, for the purpose of neural networks, function identically [8]. As a result, the illustrations in this section show cross-correlation rather than proper convolution.

As the convolution is computed over three dimensions, both the input image and the kernel are, in the general case, three-dimensional [29]. Like two-dimensional convolution, three-dimensional convolution is performed by sliding a kernel over the image. The main difference is the added depth, meaning that a convolution of a depth-three kernel and a depth-three image effectively performs three two-dimensional convolutions, one for each depth channel [31]. The contributions of the three channels are summed up, a bias added

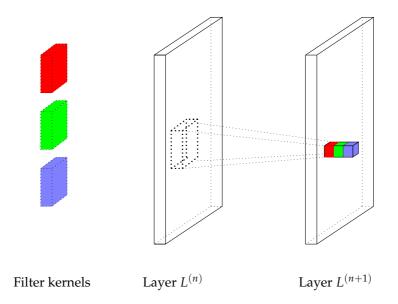

Figure 2.17: Several three-dimensional filter kernels used to produce multiple depth channels in layer  $L^{(n+1)}$ . The dotted outline in layer  $L^{(n)}$  is the position to which each of the kernels is to be applied. The red, green and blue kernels are applied separately and the output of each application is used for a separate depth channel in layer  $L^{(n+1)}$ .

and the result passed through a non-linear activation function [30] such as the ReLU. The non-linearity introduced by the activation function is what allows the network to "learn" [8]. More formally, the non-linearity allows the network to approximate any arbitrary mathematical function [32]. The output of the activation function is used as the contribution to the convolved feature [30]. The entire procedure for a single spatial position is shown in Fig. 2.18. Here, the convolution of each depth channel is shown as a separate two-dimensional convolution.

Despite convolutional layers theoretically performing a three-dimensional convolution, the feature maps of the input are typically treated separately [33]. This is sometimes referred to as depthwise convolution wherein independent, two-dimensional convolution is applied to each depth channel [34]. As a result, computing the activation of neuron  $h_{i,j,k_n}^{(n)} \in \mathbb{R}$  at position (i, j) in depth channel  $k_n \in \mathbb{Z}^+$ ,  $k_n \leq d_n$  of layer  $L^{(n)}$  can be summarized as

$$h_{i,j,k_n}^{(n)} = \Phi\left(\sum_{k_{n-1}} \left(f_{k_n}^{(n)} * h_{k_{n-1}}^{(n-1)}\right)_{i,j} + b_{i,j,k_n}^{(n)}\right)$$

(2.23)

where  $\Phi : \mathbb{R} \to \mathbb{R}$  denotes an arbitrary activation function and  $b_{i,j,k_n}^{(n)} \in \mathbb{R}$  the bias for position (i, j) of depth channel  $k_n$ . The term  $(f_{k_n}^{(n)} * h_{k_{n-1}}^{(n-1)})_{i,j}$  is the value at position (i, j) of the convolved feature resulting from the two-dimensional convolution of filter kernel  $f_{k_n}^{(n)}$  and the activation  $h_{k_{n-1}}^{(n-1)}$  of layer  $L^{(n-1)}$ . The summation is performed over the respective depth channels  $k_{n-1} \in \mathbb{Z}^+$ ,  $k_{n-1} \leq d_{n-1}$  of layer  $L^{(n-1)}$ . The layer transforms from  $d_{n-1} \in \mathbb{Z}^+$  depth channels in layer  $L^{(n-1)}$  to  $d_n \in \mathbb{Z}^+$  channels in layer  $L^{(n)}$ .

The number of feature maps produced by a convolutional layer is determined by the number of kernels used [29]. This is not necessarily chosen to keep the number of depth channels constant between layers. As an example, the first convolutional layer in the well-known AlexNet scales the number of depth channels from 3 to 48 by applying  $48 \ 11 \times 11 \times 3$

Figure 2.18: Three-dimensional cross-correlation with added bias. ReLU is used as the activation function. The notation A(:,:,n) signifies depth channel  $n \in \mathbb{Z}_0^+$ ,  $n \leq 2$  of order-three tensor A. The kernel is slid over the image and at each position the cross-correlation between the kernel and the image is computed. This is done in a per-channel fashion, meaning kernel depth channel 0 is applied to image depth channel 0, kernel channel 1 is applied to image channel 1 and so on. The sum of the contributions of the depth channels is added with the bias. This sum is passed through the ReLU activation function and the output placed in the feature map.

convolution kernels with a stride of 4 to the input image. The second layer scales the depth up even further by applying  $1285 \times 5 \times 48$  convolution kernels [25].

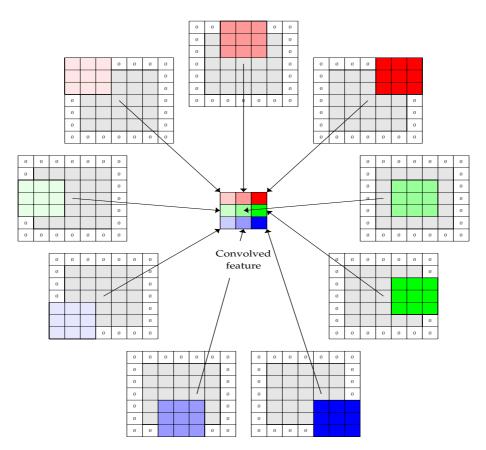

#### 2.3.3 Max-Pooling Layer

Pooling layers are commonly inserted between successive convolutional layers in order to progressively reduce the spatial extent of the data [26]. The common form max-pooling replaces a certain location of the input with the maximum intensity of the area [8]. The operation is extended to higher dimensions by applying independent two-dimensional max-pooling to each depth channel [26]. Fig. 2.19 shows this for a depth-three image.

The output of the pooling layer is controlled by the size of the kernel and the stride between kernel applications. The most common choice is to apply a  $2 \times 2$  kernel with a stride of 2. With these choices, four pixels in the input are replaced with a single, reducing the amount of data by 75% [26].

Pooling is beneficial not only for increasing computational speed, it also makes the network approximately invariant to smaller translations in its input. This means that even if the input is translated a small distance, most of the outputs of the pooling layer remain the

Figure 2.19: Max-pooling of an image with 3 depth channels using a  $2 \times 2$  kernel applied with a stride of 2. The max operation is applied independently to each depth channel and the result stored in the corresponding depth channel in the output. The colored cells in the output correspond to the  $2 \times 2$  area with the same color in the image.

same [8]. The approximate translation invariance is illustrated in Fig. 2.20. Pooling also allows for increasing the receptive field of the network, meaning that the information under the kernel is derived from a larger area. While the receptive field can be increased also by making the network deeper, the per-layer increase obtained by applying pooling is larger than that of adding additional convolutional layers [35]. Additionally, the downsampling itself is directly beneficial as it means that the inputs of subsequent layers are smaller, reducing the number of weights required by the network [36].

#### 2.3.4 Fully Connected Layer

Fully connected layers are most commonly used as the last layer of convolutional neural networks [17], although they may less frequently appear earlier as well [36]. In a fully connected layer, each neuron is connected to all neurons in the prior layer [30]. This means that fully connected layers in convolutional networks, much like the layers in feedforward networks, perform a per-neuron scaling. It is common that the large number of parameters required for this scaling is the main contributor to the steep memory requirements of convolutional networks [36]. Examples of this include the AlexNet, which consists of five convolutional layers and three fully connected layers [25]. In this network, 58 000 000 of a total of 60 000 000 parameters correspond to fully connected layers [36]. In the VGG16 network, consisting of

Figure 2.20: Illustration of the approximate translation invariance of max-pooling. The upper image shows the result of applying max-pooling with a  $3 \times 1$  kernel. In the lower image, the input has been shifted down one step. Despite the change in the input, large parts of the output remain the same.

thirteen convolutional layers and three fully connected ones [24], 123 000 000 of the 138 000 000 total parameters are found in fully connected layers [36].

Convolutional networks are constructed predominantly such that the convolutional or pooling layer directly preceding a fully connected layer in the network outputs an order-one tensor. This is sometimes referred to as flattening [18] and allows for evaluating the fully connected layer as a matrix-vector operation [37]. As an example, the activations  $h_j^{(n)} \in \mathbb{R}$ , j = 1, 2, 3 of the fully connected layer  $L^{(n)}$  shown in Fig. 2.21 may be evaluated as

$$\begin{bmatrix} h_{1}^{(n)} \\ h_{2}^{(n)} \\ h_{3}^{(n)} \end{bmatrix} = \Phi \left( \begin{bmatrix} w_{1,1}^{(n)} & w_{1,2}^{(n)} & w_{1,3}^{(n)} \\ w_{2,1}^{(n)} & w_{2,2}^{(n)} & w_{2,3}^{(n)} \\ w_{3,1}^{(n)} & w_{3,2}^{(n)} & w_{3,3}^{(n)} \end{bmatrix} \begin{bmatrix} h_{1}^{(n-1)} \\ h_{2}^{(n-1)} \\ h_{3}^{(n-1)} \end{bmatrix} + \begin{bmatrix} w_{0,1}^{(n)} \\ w_{0,2}^{(n)} \\ w_{0,3}^{(n)} \end{bmatrix} \right)$$

(2.24)

where  $\Phi : \mathbb{R} \to \mathbb{R}$  is an arbitrary activation function. Here,  $h_i^{(n-1)} \in \mathbb{R}$ , i = 1, 2, 3 is the activation of the *i*<sup>th</sup> neuron in layer  $L^{(n-1)}$  in Fig. 2.21. The elements of the  $3 \times 3$  matrix are the layer weights  $w_{i,j}^{(n)} \in \mathbb{R}$  and rightmost vector consists of the layer biases  $w_{0,i}^{(n)} \in \mathbb{R}$ .

#### 2.4 Data-Level Parallelism

Data-level parallelism is a parallel programming model that relies on vectorization techniques to increase program throughput [38]. Rather than scheduling instructions over multiple logical threads of control, it relies on multiple compute units performing the same operation on different data items. The approach is used in GPUs [39] where billions of pixels are processed independently of each other [40].

Figure 2.21: A fully connected layer  $L^{(n)}$  and its input layer  $L^{(n-1)}$ , both with their respective neurons arranged in columns.

When compared to concurrency, data-level parallelism has both advantages and shortcomings. Concurrent programming relies on scheduling a potentially large number of logical threads over a fixed number of physical cores. Which threads are run on which core is decided by the operating system scheduler [41]. This task scheduling is often both difficult and computationally expensive [42]. Additionally, sharing data between multiple threads introduces the risk of encountering race conditions [43]. As data parallelism does not rely on threads, it does not suffer from these drawbacks. Its main disadvantages are instead that it generally requires well-structured data access and has limited support for branching [44].

#### 2.4.1 SIMD